-

英特尔计划通过堆叠纳米片晶体管 来大幅提高芯片中晶体管的数量

目前手机芯片的制程工艺已经达到了5nm这一突破,随后的3nm甚至1nm都是一个非常巨大的挑战,这些nm级参数越小,代表着单位面积上容纳的晶体管数量就越多。不过这些数量总会限制于平铺在硅晶片上晶体管的体积,一旦晶体管体积到达了可以缩小的临界值,那么是否意味着芯片的发展将会停滞不前呢?

就在本周的IEEE国际电子设备会议上,英特尔提供了一种新的能够拓展晶体管数量的思路。

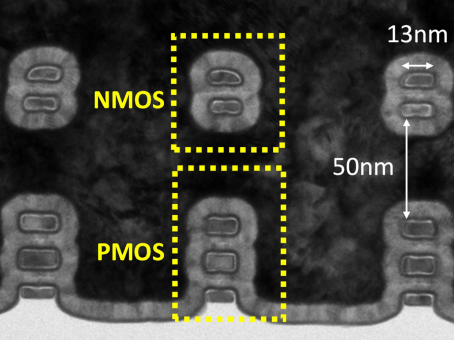

这些平铺在硅晶片上的晶体管,包括了两种MOS晶体管,使用N型金属的MOS晶体管称为NMOS晶体管,使用了P型金属的MOS晶体管称为PMOS晶体管。这两种晶体管组合成如今逻辑电路不可或缺的CMOS电路,也就是互补电路,仅需一点电流就可以发生变化因而降低功耗。

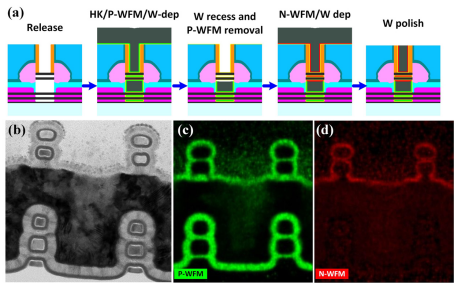

追求更高制程工艺的结果就是这两个晶体管需要无限靠近,但是此前研究人员仅仅只是在x和y轴上去做平面设计,而如今英特尔打算利用芯片的Z轴,其使用的基础就是被认为是下一代晶体管结构的纳米片。

英特尔的研究人员先是用这种思路设计了一个简单了逻辑电路,该电路仅需要两个晶体管,一个输出一个输入,通过堆叠式摆放后比并排排放占用面积缩小了一半。为此英特尔开发了一种自对准工艺,用于在相同步骤中构建的两种电路在晶圆粘合时发生偏移从而导致出现故障。

英特尔目前的主要目标是将制作流程尽可能的简化,如果工艺太过复杂,将会影响这种堆叠式晶体管的实用性,然后再追求性能。这种能够使晶体管数量翻倍的技术,一旦成熟,对于目前的芯片设计又将是一个巨大的技术革新。

欢迎关注智八斗网官方微信:智八斗(ZBDTVcom) 专注消费领域原创短视频,精选最热科技资讯。

-

推荐阅读

-

相关文章

本栏目的其他文章

热门排行

- 本周

- 本月